随着微波通信技术的快速发展,对接收机的灵敏度要求越来越高,作为各类接收机的心脏,频率源需要为其提供高性能的本振信号,它的相位噪声指标成为制约接收机性能的关键因素之一。为了改善频率源的相噪,国内外很多公司和科研机构开展了很多这方面的研究,也提出了各种有效的方法。这些方法有的从构成锁相环的相位噪声来源直接分析,更多的从实现方式来分析,包括新型直接合成、DDS和锁相环芯片混合技术、自偏置、谐波混频、新型多级自谐波混频和级联式偏置、混频环等。频率综合器的使用场所:无线电通信、计算机时钟发生器、信号处理、精密测量、雷达、光通信等。dds频率综合器9kHz至43.5GHz可设

频率合成器的基本组成:采用锁相环(PLL)功能组成的频率合成器,每个频率合成环路一般包括:基准时钟振荡器、相位比较器、低通滤波器、压控振荡器和可预置分频器。频率合成器的基本工作过程:VCO频率的稳定过程和VCO频率的变频过程。将一个高稳定度和高精度的标准频率,经过功能电路的作用,产生具有同样稳定度和精确度的大量离散频率的技术称为频率合成技术。根据该原理组成的设备或仪器称为频率合成器(或频率综合器)。AnaPico频率综合器dds频率综合器9kHz至43.5GHz可设频率综合器在调制解调、射频发射和接收、时钟生成和数字信号处理等方面。

频率综合器的工作原理分别是:直接模拟合成法、锁相环合成法和直接数字合成法。直接模拟合成法利用倍频、分频、混频及滤波,从单一或几个参数频率中产生多个所需的频率。该方法频率转换时间快(小于100ns),但是体积大、功耗大,已基本不被采用。锁相环合成法通过锁相环完成频率的加、减、乘、除运算。该方法结构简化、便于集成,且频谱纯度高,使用比较广,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。

随着各种新技术的不断涌现,在无线电技术的应用中,频率综合技术是比较新的发展技术。尤其是频率综合方式和频率综合器的出现,将其优势进行发挥,尤其是频率综合器在雷达方面的应用越来越广。频率综合器的研究背景频率综合器如同雷达的心脏,在性能的优劣程度上直接影响雷达的应用。因此,对于频率综合器的性能是具有一定的特性和要求的,主要是稳定性和噪音的要求。随着无线电技术的发展,电路工艺的技术不断完善,在频率综合器中,需要把控可靠性能。频率综合器通常在无线电、通信和计算机领域中使用。

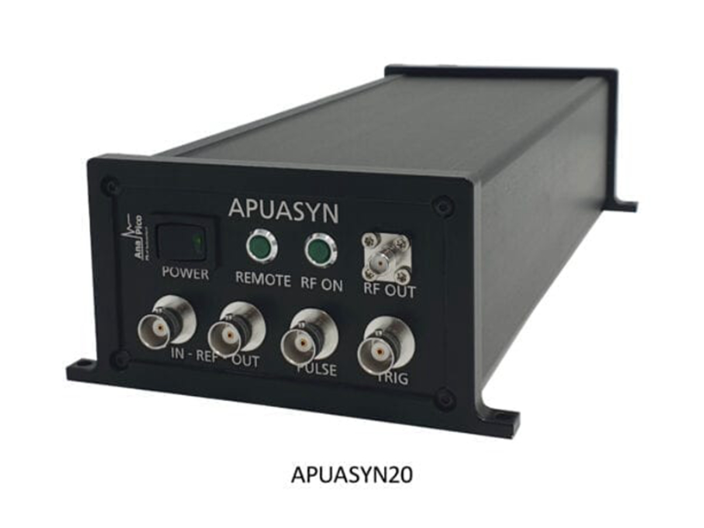

一种降低小数分频杂散的聪明的做法是利用一个可变参考频率。该技术基于一个小数N分频综合器的杂散的位置是其特定分频比和输出频率的函数的原理。因此,对于一个给定的输出频率,可以通过改变参考频率和相应的分频比的方式来移动(然后过滤掉)一个不想要的杂散。这涉及到频率规划,因此需要一个额外的频率综合器(用作参考频率)。此外尽管减小了分频比,其依然可能大到影响PLL性能。Anapico始终秉承瑞士制造的精神,坚持为用户提供精密的产品,主要产品包括射频微波信号源、相位噪声分析仪、频率综合器等,并在量子物理,5G通信、雷达和卫星等射频微波领域为用户提供测试测量解决方案。 AnaPico频率综合器可在1U机箱内输出4路相参但单独可控的高质量连续波和脉冲调制信号。dds频率综合器9kHz至43.5GHz可设

频率综合器模块可以通过调制输入信号的频率来产生调频信号、调幅信号等。dds频率综合器9kHz至43.5GHz可设

可预置分频器在频率合成中,为了提高控制精度,鉴相器在低频下工作。而VCO电路输出频率是比较高的,为了提高整个环路的控制精度,离不开分频技术。分频器输出的信号送到相位比较器,和基准时钟信号进行相位比较。VCO电路在锁相环中比较重要,是频率合成及锁相环路的重要电路。它应满足这样一些特性:输出幅度稳定性要好,在整个VCO电路工作频带内均应满足此要求,否则会影响鉴相灵敏度;频率覆盖范围要满足要求且有余量;电压-频率变换特性的线性范围要宽。dds频率综合器9kHz至43.5GHz可设