- 品牌

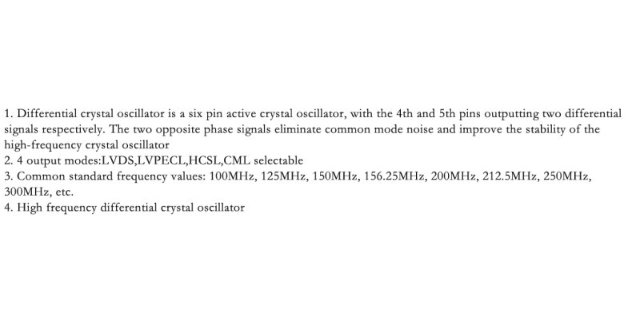

- 华昕

- 型号

- 7S025000VEL

- 频率特性

- 高频

- 封装材料

- 金属

- 外形

- 贴片式

- 标称频率

- 156.25

- 调整频差

- 156.25

- 基准温度

- -40~+85

- 负载谐振电阻

- 0.005

- 温度范围

- -40~+85

- 产地

- 中国

- 厂家

- 华昕

- 封装尺寸

- 7.0*5.0

- 类型

- 差分晶振

- 输出模式

- LVDS

- 电压

- 3.3V

差分晶振的抗冲击能力探讨差分晶振,作为一种高精度、高稳定性的振荡器,广泛应用于各种电子设备和系统中。在复杂多变的工作环境中,差分晶振的抗冲击能力显得尤为重要。那么,差分晶振的抗冲击能力如何呢?首先,我们需要了解差分晶振的基本结构和工作原理。差分晶振由石英晶体和振荡电路组成,通过石英晶体的压电效应产生稳定的振荡信号。这种结构决定了差分晶振具有较高的机械强度和抗震性能。其次,差分晶振在设计和制造过程中,会经过严格的测试和筛选。例如,通过高低温循环测试、冲击测试等,确保产品在各种恶劣环境下仍能保持稳定的性能。这些测试不仅提高了差分晶振的抗冲击能力,还延长了其使用寿命。此外,差分晶振还采用了一些特殊的保护措施。例如,在晶振外壳内部填充减震材料,减少外部冲击对晶振的影响;在电路设计中加入滤波电路,降低电磁干扰对晶振稳定性的影响。这些保护措施共同增强了差分晶振的抗冲击能力。综上所述,差分晶振具有较高的抗冲击能力。通过合理的结构设计、严格的测试和筛选以及特殊的保护措施,差分晶振能够在各种恶劣环境下保持稳定的性能。差分晶振的相位延迟如何?北京差分晶振分类

差分晶振功耗特性在电子设备的设计和使用中显得尤为重要。功耗的大小不仅影响设备的运行效率,还直接关系到设备的稳定性和使用寿命。特别是在追求绿色、环保、节能的现代社会,低功耗的电子元件更是备受欢迎。差分晶振的功耗与其谐振频率紧密相关。一般而言,谐振频率越高,晶振的功耗也会相应增大。这是因为高频振动需要更多的能量来维持。相反,谐振频率较低的晶振,其功耗则会相对较小。这一特性使得在设计电路时,可以根据实际需求选择合适的谐振频率,从而达到降低功耗的目的。除了谐振频率,差分晶振的功耗还与其抖动水平有关。抖动是指晶振输出频率的稳定性,抖动水平越低,说明晶振的输出越稳定,功耗也会相应降低。因此,在选择差分晶振时,除了考虑谐振频率,还应关注其抖动水平,以确保在满足性能需求的同时,实现低功耗运行。通常情况下,差分晶振的功耗在20mA以下。但在某些高频或高稳定性的应用场景,功耗可能会超过这一范围,甚至达到100mA以上。因此,在实际应用中,需要根据具体的使用场景和需求,合理选择差分晶振的型号和参数,以实现合适的性能和功耗平衡。总的来说,低功耗的差分晶振是实现电子设备高效、稳定、节能运行的关键元件之一。福建差分晶振选型差分晶振的抗振动能力如何?

差分晶振的未来发展趋势

1、差分晶振将会继续提升其频率稳定性与精度,以满足日益严格的通信和数据传输需求。随着5G、6G等通信技术的不断演进,差分晶振的稳定性和可靠性将成为保证数据传输质量的关键。

2、小型化和低功耗将成为差分晶振发展的重要方向。随着物联网、可穿戴设备等领域的快速发展,对电子元件的尺寸和功耗要求越来越严格。差分晶振通过采用先进的封装技术和材料,有望实现更小的体积和更低的功耗,从而适应更多应用场景。

3、差分晶振还将向着多功能化和集成化的方向发展。未来的差分晶振可能不仅具有时钟信号产生功能,还可能集成温度补偿、频率调整等多种功能,从而满足复杂系统的需求。同时,差分晶振与其他电子元件的集成也将更加紧密,以提高系统的整体性能和可靠性。

4、差分晶振的智能化和可配置性也将成为发展趋势。通过引入智能算法和可配置技术,差分晶振可以根据系统的实际需求进行动态调整和优化,从而实现更高的性能和更低的功耗。

差分晶振的未来发展趋势将是频率稳定性与精度提升、小型化与低功耗、多功能化与集成化以及智能化与可配置性的完美结合。这将使得差分晶振在通信、计算机、物联网等领域发挥更加重要的作用,推动整个电子行业的持续发展。

LVDS(LowVoltageDifferentialSignaling,低电压差分信号)接口,又称为RS-644总线接口,是20世纪90年代提出的一种数据传输和接口技术。它克服了TTL电平方式在传输宽带高码率数据时功耗大、电磁干扰大的问题。采用低压和低电流驱动方式,实现了低噪声和低功耗,因此在液晶电视等需要高信号完整性和低抖动的系统中得到了广泛应用。CML(CurrentModeLogic,电流模式逻辑)则是一种常用于网络物理层传输和高速Serdes器件的接口技术。其理论极限速度可达10Gbit/s,功率更低,外部更简单。CML的输出电路形式是一个差分对,输出信号的摆幅与供电电压有关,耦合方式则根据接收器和发送器的电源配置来选择。LVPECL(LowVoltagePositiveEmitter-CoupledLogic,低电压正射极耦合逻辑)接口由ECL和PECL发展而来,使用3.3V电平。其输出结构为一对差分信号,通过电流源接地。LVPECL的差分输出端具有特定的传输阻抗和输出电平,使其在各种应用场景中都能保持稳定的性能。VML(VoltageModeLogic,电压模式逻辑)接口则具有其独特的电压特性和信号传输方式,为不同设备间的连接提供了灵活的选择。这四种接口技术各具特色,为现代电子设备提供了高效、稳定的数据传输方案。差分晶振的功耗情况如何?如何降低其功耗以提高系统能效?

差分晶振的驱动电路设计是一项关键的技术任务。差分晶振作为频率源,其驱动电路的设计直接影响到整个系统的性能。

首先,明确差分晶振的规格和参数是驱动电路设计的基础。我们需要了解差分晶振的频率范围、输出波形、功耗、尺寸等参数,以便在设计中充分考虑这些因素。根据应用需求,选择合适的差分晶振,确保其在工作环境中能够稳定输出所需频率。

其次,在驱动电路设计中,要特别注意降低寄生电容和温度的不确定性。晶振应尽量靠近芯片放置,缩短线路长度,防止线路过长导致的串扰和寄生电容。同时,对晶振周围进行包地处理,以减少对其他电路的干扰。

此外,还需考虑负载电容的回流地设计,确保回流路径短且有效。在走线设计时,应遵循一定的规则。例如,晶振底部应避免走信号线,特别是高频时钟线。走线时,应先经过电容再进入晶振,以减少对晶振的影响。对于贴片无源晶振和有源晶振,应根据其封装和引脚类型选择合适的走线方式。

差分晶振的驱动电路设计还需要考虑电源和负载条件。选择合适的电源和负载规格,以确保差分晶振在工作过程中具有足够的稳定性和可靠性。

综上所述,差分晶振的驱动电路设计是一项综合性的技术任务,需要综合考虑多个方面的因素。 差分晶振的主要应用场景有哪些?福建差分晶振选型

差分晶振与普通晶振有何区别?北京差分晶振分类

差分晶振的负载效应对性能的影响

负载效应指的是差分晶振的输出端所连接的外部电路对其性能产生的影响。当差分晶振的输出端连接的负载电容、负载电阻等参数发生变化时,其输出频率和稳定性都可能受到影响。这是因为负载的变化会改变差分晶振内部的谐振条件,从而影响其工作状态。

首先,负载效应对差分晶振的输出频率具有明显影响。当负载电容或负载电阻增加时,差分晶振的输出频率可能会下降;反之,当负载减小时,输出频率可能上升。这种频率变化可能导致系统工作不正常,甚至引发故障。

其次,负载效应还会影响差分晶振的稳定性。稳定性是差分晶振的重要性能指标之一,它决定了输出频率的准确性和长期稳定性。负载的变化可能导致差分晶振的稳定性下降,使其输出频率产生漂移或抖动,进而影响整个系统的性能。

为了减小负载效应对差分晶振性能的影响,可以采取以下措施:首先,在设计电路时,应尽量选择与差分晶振匹配的负载电容和负载电阻,以保证其工作在比较好状态;其次,可以采用缓冲放大器或驱动电路来隔离外部电路对差分晶振的影响;,定期对差分晶振进行校准和维护,以确保其性能的稳定性和准确性。综上所述,差分晶振的负载效应对其性能具有重要影响。 北京差分晶振分类

差分晶振的启动时间分析差分晶振,其启动时间对于设备的整体性能有着重要影响。那么,差分晶振的启动时间究竟需要多久呢? 首先,我们要明确晶振的启动时间是指从刚刚接上电源开始,到晶振可正常工作所需要的时间。这个时间的长短取决于多种因素。电容的充电时间是影响晶振起振时间的一个重要因素。在晶振电路中,外部电容的充电时间越长,晶振起振时间也就越长。因此,优化电容的选择和电路设计,可以有效缩短晶振的启动时间。此外,晶振管自身的参数,如内部电容、电感、阻抗等,也会对启动时间产生影响。这些参数的优化,同样有助于缩短启动时间。外部环境中的干扰也是影响晶振启动时间不可忽视的因素。例如,电源电压的波动、环境...

- 济南差分晶振选型 2024-12-03

- LVDS差分晶振输出波形 2024-11-24

- 黄石125M差分晶振 2024-11-16

- 江西LVDS差分晶振 2024-11-08

- 100M差分晶振输出模式 2024-10-20

- 江西差分晶振推荐 2024-10-11

- 广西6脚差分晶振 2024-09-17

- 河南差分晶振型号 2024-09-13

- 120M差分晶振温度系数 2024-09-12

- 工业级差分晶振价格 2024-09-10

- 耐高温差分晶振批发 2024-09-02

- 武汉差分晶振电压 2024-08-31

- 福建差分晶振选型指南 2024-08-29

- 山西低功耗差分晶振 2024-08-28

- 武汉LVPECL差分晶振 2024-08-26

- 3225差分晶振多少钱 2024-08-25

- 封装贴片晶振样品 12-21

- 高精度无源晶振供应商 12-20

- 爱普生32.768KHZ晶振定制 12-20

- 40MHZ华昕晶振选型指南 12-19

- 合肥贴片热敏晶振 12-19

- 有源8MHZ晶振价格咨询 12-18

- 封装24MHZ晶振排名 12-18

- KDS25MHZ晶振供应商 12-17

- 宽温26MHZ晶振频率稳定性 12-17

- 38.4MHZ华昕晶振优势 12-16