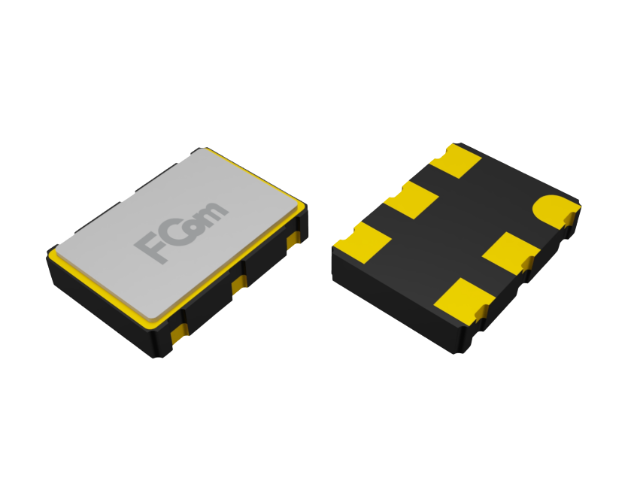

- 品牌

- FCom富士晶振

- 型号

- FCO-L-PG

- 系列

- FCO-L-PG

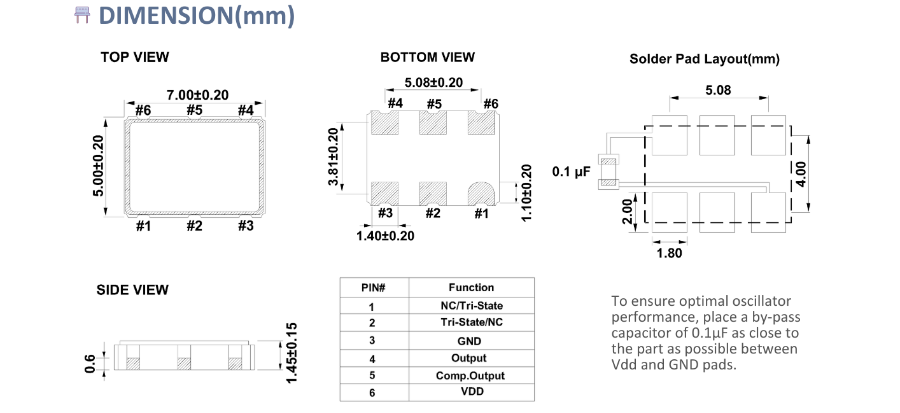

- 类型

- MHz晶体

- 频率范围

- 10 MHz ~ 220 MHz

- 工作电压

- 1.8V / 2.5V / 3.3V 可选

- 温度频差

- ±25ppm / ±50ppm(出厂可选)

- 工作温度

- –40°C ~ +105°C

- 相位抖动

- 0.2 ~ 0.6ps RMS(12kHz~20MHz)

LVDS、HCSL输出接口可根据交换芯片与PHY芯片对输入特性的不同灵活匹配,提升时钟驱动与线性传输能力。特别在40G/100G/400G以太网平台中,FCom差分振荡器能够在长距离走线条件下保持低抖动输出,避免频率飘移或信号退化。 FCom产品还支持“频率冗余模式”,在主通道晶振异常时切换至备份频率,保障关键控制板不中断运行,增强设备整体容错能力。该特性已在多款云数据中心交换平台中验证,成为网络高可用性设计的重要组成。网络交换芯片中的时钟冗余与接口兼容性。FCom富士晶振网络交换芯片中的时钟冗余与接口兼容性卫星通信终端中各个方面采用可编程差分振荡器输出基频。抗干扰可编程差分振荡器是什么

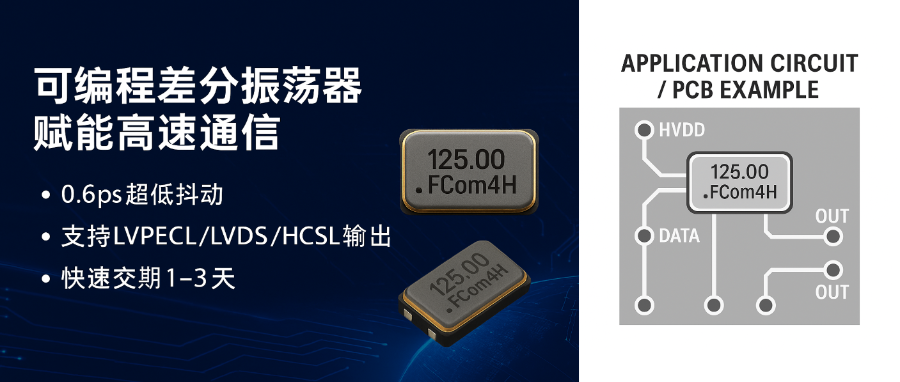

可编程差分振荡器

FCom产品通过可编程方式设定多个差分输出接口,支持同时输出两个频点,或配置成冗余容错双接口。在高密度PCB板上,其低抖动性能可避免误码率激增,增强时钟边缘的相位清晰度,为主板信号质量提升打下基础。 此外,主板厂商在设计中常因芯片选型变更而临时调整参考频率,传统振荡器无法灵活响应,FCom的可编程特性则使其可通过配置实现快速频率切换,缩短调试周期。产品封装支持标准7050,具备优异的热导率,有利于在服务器运行高负载下保持器件长时间稳定。有什么可编程差分振荡器产品介绍可编程差分振荡器已成为前沿通信平台的标准配置。

大规模FPGA设计项目中的统一时钟架构构建 在通信基站、图像处理平台、测试测量设备、AI网关等多个场景中,FPGA作为关键处理单元需同时管理多个时钟域(输入同步、IO驱动、PLL控制、AXI总线),设计中存在频率出错、资源浪费与同步偏移风险。FCom富士晶振可编程差分振荡器提供统一频率源与灵活配置方式,为大规模FPGA设计提供集中管理的可控时钟结构。 FCom产品支持多频输出(如24MHz、50MHz、100MHz、125MHz、156.25MHz、200MHz),具备LVDS/HCSL多接口配置能力,可连接至FPGA外部时钟输入口、IO Bank参考时钟、PLL Clock-IN与内部逻辑触发器。输出抖动低至0.1ps,保障时序余量。 通过FCom提供的GUI工具,用户可快速配置目标频率组合并仿真接口兼容性,提升工程调试效率。产品支持1.8V~3.3V工作平台,适应不同FPGA品牌(Xilinx、Intel、Lattice、Microchip等)IO电压标准。

可编程差分振荡器是一类支持频率灵活配置、输出接口兼容性强、抖动控制能力优异的高性能晶体振荡器,各个方面应用于需要高速、高稳定性时钟源的系统中。与传统固定频点晶振不同,可编程差分振荡器具备频率定制能力,通过I²C或OTP方式可编程设置输出频率、接口类型及相位特性,极大提升系统设计灵活度。FCom富士晶振推出的可编程差分振荡器系列产品,充分结合差分输出(LVDS、HCSL、LVPECL)优势与可配置特性,满足5G通信、AI服务器、数据中心网络、SerDes链路等前沿时钟需求。 FCom的可编程差分振荡器支持宽频输出范围(10MHz~250MHz),频率步进精确至10kHz,适配各种主流通信协议如PCIe、SATA、QSFP、IEEE1588、SyncE等。输出抖动指标优于0.15ps RMS(12kHz~20MHz范围),部分型号可提供0.05ps极限低抖动选项,确保高速信号系统中的时钟纯净度和误码率控制能力。可编程差分振荡器输出稳定、启动快速,性能可靠。

前沿视频会议系统中的多模时钟源统一方案 随着远程办公、分布式协作与高清视频会议的迅猛发展,视频会议终端系统集成了音频处理、高清视频采集、智能编解码、网络传输、触控控制等多模处理能力。系统内部存在多个异步模块与高带宽接口,对时钟输出提出“多频点、高稳定性、低抖动”的统一管理要求。FCom富士晶振推出的可编程差分振荡器,具备高度定制化与低功耗特性,为会议终端实现高一致性的统一时钟平台。 产品可输出27MHz、74.25MHz、100MHz、125MHz、148.5MHz、156.25MHz等视频与通信标准频点,通过LVDS或HCSL差分输出连接视频ISP、编解码SoC、USB 3.0控制器与网络PHY芯片。抖动控制在0.1ps以下,确保帧同步稳定、音画一致、数据无断裂。 FCom可编程振荡器具备动态启停、频率切换与OE控制能力,支持触发式待机、会议开始后自动启用全部频点等模式,进一步降低待机功耗与误发热。 产品封装适配主板与模组双部署形式,兼容BGA主控平台与多模接口模组。已被多家会议终端、智能音视频一体机厂商各个方面采用,成为高清视频流同步的底层时钟支撑。可编程差分振荡器各个方面应用于服务器、交换机和网卡。有什么可编程差分振荡器产品介绍

可编程差分振荡器适用于各种工业、网络和通信环境。抗干扰可编程差分振荡器是什么

在实际部署中,FCom差分振荡器可作为PCIe Root Complex参考时钟、10G以太网PHY/SerDes、Thunderbolt通道主时钟等使用,通过可编程接口轻松配置至100MHz、125MHz、156.25MHz等常用频率点,亦支持中间值(如106.25MHz、161.1328MHz)定制频率,适用于特定链路协议时钟源。 与传统固定晶振方案相比,FCom可编程振荡器在SerDes测试中展现更优误码率控制与稳定锁相性能,尤其在信号完整性检测(如Eye Diagram、BER分析、ISI测试)中更具优势,是信号链质量设计的重要一环。抗干扰可编程差分振荡器是什么

- FCO3LPG可编程差分振荡器客服电话 2026-02-14

- 优势可编程差分振荡器电话 2026-02-10

- 低抖动可编程差分振荡器联系方式 2026-02-08

- 7050可编程差分振荡器有哪些 2026-02-08

- 低抖动可编程差分振荡器常见问题 2026-02-07

- 抗干扰可编程差分振荡器是什么 2026-02-07

- FCO3LPG可编程差分振荡器一般多少钱 2026-02-06

- 国产可编程差分振荡器销售价格 2026-02-06

- 高频可编程差分振荡器客服电话 2026-02-06

- 高频稳定可编程差分振荡器售后服务 2026-02-05

- 可编程可编程差分振荡器售后服务 2026-02-05

- 高频可编程差分振荡器制造价格 2026-02-04